Nhờ khả năng tích hợp cao, một bo mạch HDI có thể thay thế cho nhiều bo mạch riêng lẻ trước đây trong cùng một thiết bị, giúp giảm kích thước sản phẩm, tăng hiệu năng và độ tin cậy của hệ thống.

Mạch HDI thường có nhiều lớp, cấu trúc ép lớp phức tạp và sử dụng cho các sản phẩm có giá trị cao. Tuy nhiên, so với mạch PCB thông thường, mạch HDI đòi hỏi quy trình thiết kế, chế tạo và lắp ráp khắt khe hơn, bao gồm các lỗ via siêu nhỏ (microvia), ép nhiều lần, căn chỉnh chính xác và kiểm soát chất lượng nghiêm ngặt.

Do đó, PCB HDI thường đi kèm với:

- Chi phí sản xuất cao hơn

- Yêu cầu thiết kế phức tạp hơn

- Khó khăn hơn trong sửa chữa (rework)

- Nhiều thách thức về khả năng sản xuất hàng loạt (DFM/DFT)

1. Các khuyến nghị khi thiết kế mạch HDI

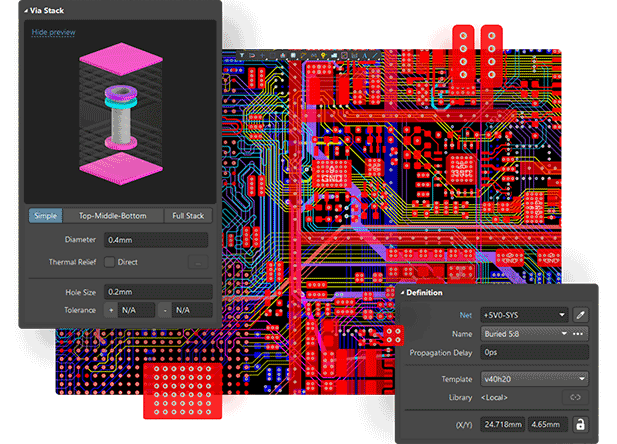

Hình 2. Minh họa layout mạch HDI dùng trong lĩnh vực IOT

1.1. Lựa chọn loại via phù hợp để giảm độ phức tạp của quy trình

Việc lựa chọn loại lỗ via là yếu tố then chốt vì nó quyết định thiết bị cần sử dụng, các công đoạn sản xuất, thời gian gia công và chi phí phát sinh. Sử dụng microvia, blind via hoặc buried via có thể giúp giảm số lớp mạch và chi phí vật liệu. Tuy nhiên, việc lựa chọn giữa via xuyên lỗ (through-hole via), via dog-bone hay via-in-pad sẽ ảnh hưởng trực tiếp đến mức độ phức tạp của toàn bộ quy trình chế tạo và lắp ráp từ đó ảnh hưởng trực tiếp đến giá thành.

1.2. Tối ưu số lượng và chủng loại linh kiện cho ứng dụng HDI

Việc lựa chọn linh kiện luôn quan trọng, nhưng đối với PCB HDI thì mang tính quyết định. Linh kiện sẽ chi phối độ rộng đường mạch, bố trí layout, loại và kích thước lỗ khoan, cũng như cấu trúc stack-up tổng thể. Bên cạnh yêu cầu về hiệu năng, cần đặc biệt xem xét kiểu đóng gói (package), khả năng truy xuất nguồn gốc, tính sẵn có và ổn định chuỗi cung ứng. Việc thay đổi linh kiện hoặc thiết kế lại layout muộn có thể làm tăng đáng kể thời gian sản xuất và chi phí vật tư.

1.3. Giảm ứng suất cơ học và nhiễu điện từ (EMI) khi bố trí linh kiện

Bố trí via không đối xứng có thể tạo ra ứng suất không đồng đều, dẫn đến cong vênh bo mạch và làm giảm tỷ lệ đạt (yield). Mật độ linh kiện cao và các đường tín hiệu công suất lớn có thể gây nhiễu điện từ (EMI), ảnh hưởng đến chất lượng tín hiệu. Ngoài ra, điện dung và điện cảm ký sinh giữa các pad và chân linh kiện đặt gần nhau cũng có thể làm suy giảm tính toàn vẹn tín hiệu (Signal Integrity).

Vì vậy, mô phỏng EMI/SI ngay từ giai đoạn thiết kế là yêu cầu rất quan trọng đối với PCB HDI.

1.4. Tối ưu đi dây để giảm các vấn đề về toàn vẹn tín hiệu (Signal Integrity)

Một trong những ưu điểm lớn của PCB HDI là khả năng sử dụng đường mạch hẹp để truyền tín hiệu, từ đó giảm kích thước bo mạch. Tuy nhiên, độ rộng đường mạch phải được thiết kế phù hợp nhằm đảm bảo toàn vẹn tín hiệu.

Trong quá trình routing, cần chú trọng:

- Giữ chiều dài đường tín hiệu ngắn nhất có thể

- Duy trì trở kháng đồng nhất trên toàn tuyến

- Bố trí mặt phẳng mass (ground plane) đầy đủ và liên tục

- Tách biệt hợp lý giữa tín hiệu số, tín hiệu tương tự và nguồn

Những nguyên tắc này giúp hạn chế suy hao, phản xạ và xuyên nhiễu, đặc biệt quan trọng đối với HDI tốc độ cao và mật độ cao.

1.5. Lựa chọn cấu trúc stack-up để tối ưu chi phí vật liệu

Bên cạnh việc lựa chọn loại via, cấu trúc stack-up cũng có ảnh hưởng rất lớn đến chi phí chế tạo PCB HDI. Loại vật liệu và số lớp mạch sẽ quyết định số chu kỳ ép lớp (lamination) và khoan (drilling/laser drilling) cần thực hiện. Đây là các công đoạn có chi phí cao trong sản xuất HDI. Do đó, chi phí phải được xem là một tiêu chí quan trọng khi thiết kế stack-up, bên cạnh các yêu cầu về điện, cơ và độ tin cậy.

2. Ưu điểm của mạch HDI

2.1. Độ tin cậy cao hơn

Nhờ tỷ lệ chiều sâu/đường kính nhỏ (aspect ratio thấp), microvia có độ tin cậy cao hơn đáng kể so với lỗ xuyên (through-hole via) truyền thống. Microvia có độ bền cơ học tốt hơn, sử dụng vật liệu và công nghệ chế tạo tiên tiến, từ đó mang lại hiệu năng và độ ổn định vượt trội.

2.2. Cải thiện toàn vẹn tín hiệu (Signal Integrity)

Công nghệ HDI ứng dụng via-in-pad và blind via, cho phép bố trí linh kiện gần nhau hơn, từ đó rút ngắn đáng kể chiều dài đường truyền tín hiệu. HDI cũng loại bỏ các đoạn “stub” do lỗ xuyên gây ra, giúp giảm phản xạ tín hiệu và cải thiện chất lượng truyền dẫn. Nhờ đó, đường tín hiệu ngắn hơn giúp nâng cao rõ rệt toàn vẹn tín hiệu, đặc biệt quan trọng với các thiết kế tốc độ cao, tần số cao.

2.3. Hiệu quả chi phí tổng thể

Khi được thiết kế và hoạch định hợp lý, công nghệ HDI có thể giảm tổng chi phí hệ thống so với PCB truyền thống, nhờ:

- Giảm số lớp mạch cần thiết

- Giảm kích thước bo mạch

- Giảm số lượng PCB phải sử dụng trong một thiết bị

2.4. Thiết kế nhỏ gọn (Compact Design)

Việc kết hợp blind via và buried via giúp giảm đáng kể không gian chiếm dụng trên bo mạch, cho phép thiết kế sản phẩm mỏng hơn, nhỏ hơn với độ tích hợp cao hơn.

2.5. Tối ưu không gian bố trí linh kiện

Nhìn chung, công nghệ HDI cho phép bố trí linh kiện trên cả hai mặt PCB với mật độ cao hơn. Các công nghệ via tiên tiến như via-in-pad và blind via giúp giải phóng diện tích đi dây, cho phép đặt các linh kiện kích thước nhỏ sát nhau hơn. Việc giảm kích thước linh kiện và cỡ chân cho phép tăng số lượng chân I/O trong cùng một diện tích, từ đó tăng tốc độ truyền tín hiệu, đồng thời giảm đáng kể suy hao và độ trễ do giao cắt đường mạch.

3. Các loại lỗ Via trên mạch HDI

Trên mạch HDI thường sử dụng 4 loại lỗ Via:

Hình 3. Các loại lỗ Via trên mạch HDI

- Via xuyên lỗ (Through-hole via): Là loại via xuyên suốt từ lớp trên cùng đến lớp dưới cùng của PCB. Đây là dạng via truyền thống, phổ biến trong PCB thông thường.

- Via mù (Blind via): Là loại via kết nối một lớp bề mặt với một hoặc nhiều lớp bên trong, nhưng không xuyên suốt toàn bộ bo mạch.

- Via chôn (Buried via): Là loại via chỉ kết nối giữa các lớp bên trong, hoàn toàn nằm ẩn trong cấu trúc PCB và không lộ ra bề mặt.

- Microvia: Là loại via có đường kính rất nhỏ (thường được khoan bằng laser), nhỏ hơn nhiều so với via xuyên lỗ. Microvia được sử dụng phổ biến trong PCB HDI để kết nối nhiều lớp mạch mà không làm tăng kích thước bo mạch, cho phép đạt mật độ liên kết rất cao.

4. Lựa chọn vật liệu gia công mạch HDI

Việc lựa chọn vật liệu và cấu trúc lớp mạch đóng vai trò then chốt trong thiết kế và sản xuất PCB HDI (High-Density Interconnect). Quá trình thiết kế liên kết HDI đòi hỏi kỹ sư phải hiểu rõ các thách thức liên quan đến việc chỉ định các vật liệu điện môi gia cường sợi thủy tinh, bao gồm đặc tính cơ – nhiệt – điện và khả năng gia công. Một số loại vật liệu phổ biến thường dùng chế tạo mạch HDI bao gồm:

- Copper Clad Laminate (CCL) – Vật liệu laminate phủ đồng: CCL là vật liệu được tạo thành bằng cách ép dán lá đồng lên một hoặc hai mặt của lớp điện môi đã đóng rắn (C-stage). Các loại CCL cứng (rigid) thường bao gồm FR-4, FR-5 hoặc một số vật liệu PTFE. Trong ứng dụng điển hình, laminate phủ đồng một mặt thường được sử dụng, trong đó lớp đồng đóng vai trò là lớp mạch ngoài, còn lớp điện môi C-stage được ép dán lên cấu trúc lõi (sub-composite).

- Resin Coated Copper (RCC) – Đồng phủ nhựa: RCC là lá đồng được phủ sẵn một lớp nhựa điện môi, có thể ép trực tiếp lên lõi mạch. Các loại RCC được phân loại dựa trên khả năng gia công trong môi trường ướt (wet processable) hoặc không. Đối với RCC không gia công ướt, các microvia thường được tạo bằng công nghệ khoan plasma hoặc khoan laser, thay vì khoan cơ truyền thống.

- PP (Prepreg) – Vật liệu bán đóng rắn: Prepreg (còn gọi là B-stage, bonding sheet hoặc preg) là vải sợi thủy tinh được tẩm nhựa. Trong quá trình sản xuất prepreg, nhựa được đóng rắn một phần nhưng chưa cứng hoàn toàn. Trong quá trình ép stack-up PCB, khi được gia nhiệt, nhựa trong prepreg sẽ chảy, bám dính và liên kết lõi PCB với lá đồng hoặc các lớp vật liệu khác, tạo thành cấu trúc bo mạch hoàn chỉnh.

5. Quy trình công nghệ sản xuất mạch HDI:

Các quy trình sử dụng trong sản xuất PCB HDI khác biệt đáng kể so với PCB thông thường. Dưới đây là những công nghệ cốt lõi trong chế tạo PCB HDI và các yếu tố thiết kế cần đặc biệt lưu ý trong suốt quá trình sản xuất.

5.1. Công nghệ ép lớp nhiều lần (Sequential Lamination)

Hình 4. Công nghệ ép lớp trong chế tạo mạch HDI

Trong công đoạn ép lớp, lõi PCB được ghép với lá đồng và các lớp prepreg bằng cách tác động nhiệt và áp suất. Mức nhiệt và áp suất cụ thể sẽ thay đổi tùy theo cấu trúc bo mạch. Sau khi hoàn tất mỗi chu kỳ ép, nhà sản xuất sẽ tiến hành khoan via. Không giống PCB thông thường, PCB HDI phải trải qua quá trình ép – khoan nhiều lần liên tiếp (sequential lamination). Các chu kỳ ép tuần tự này giúp:

- Hạn chế dịch chuyển lớp

- Giảm nứt gãy khi khoan laser/microvia

- Đảm bảo độ chính xác và độ tin cậy của cấu trúc HDI nhiều lớp

5.2. Vật liệu lấp via (Via Fill Types)

Hình 5. Lỗ via được lấp trên mạch HDI và lỗ via thông thường

Vật liệu lấp via phải phù hợp với ứng dụng và yêu cầu kỹ thuật của PCB. Các loại vật liệu lấp via phổ biến trong HDI bao gồm:

- Mạ điện hóa (electrochemical plating)

- Bạc lấp via (silver-filled)

- Đồng lấp via (copper-filled)

- Keo epoxy dẫn điện

- Keo epoxy không dẫn điện

Trong thực tế sản xuất, epoxy không dẫn điện là loại được sử dụng phổ biến nhất do chi phí hợp lý và độ ổn định cao.

5.3. Công nghệ Via-in-Pad

Công nghệ via-in-pad cho phép đặt via trực tiếp trên pad linh kiện. Quy trình bao gồm:

- Khoan via

- Mạ đồng thành lỗ

- Lấp via bằng vật liệu phù hợp

- Phủ kín (capping)

- Mạ đồng bề mặt

- Hoàn thiện pad hàn

Via-in-pad thường là quy trình từ 10–12 công đoạn với độ khó cao đòi hỏi thiết bị chuyên dụng và kỹ thuật viên tay nghề cao.

5.4. Công nghệ khoan laser (Laser Drill Technology)

Các thiết kế HDI thường yêu cầu microvia khoan bằng laser. Hệ thống khoan laser hiện đại có thể tạo ra lỗ via đường kính chỉ ~20 µm, với khả năng gia công chính xác trên cả kim loại và sợi thủy tinh, tạo ra các lỗ cực nhỏ nhưng thành lỗ sạch và ổn định. Ngoài ra, việc sử dụng vật liệu có cấu trúc sợi đồng đều và hằng số điện môi thấp (low-Dk) còn giúp giảm kích thước microvia và cải thiện độ chính xác khoan.

6. Các lưu ý khi thiết kế mạch HDI

6.1. Độ rộng và khoảng cách đường mạch (Line width & spacing)

PCB HDI thường có độ rộng và khoảng cách đường mạch ≤ 1 mil. Điều này đòi hỏi kỹ thuật thiết kế chính xác và công nghệ sản xuất tiên tiến để đảm bảo:

- Đường mạch được hình thành đúng biên dạng

- Không xảy ra ngắn mạch

- Hạn chế nhiễu và xuyên nhiễu giữa các trace

6.2. Kích thước và vị trí via (Via size & placement)

PCB HDI sử dụng phổ biến microvia (đường kính ≤ 6 mil). Microvia khó khoan và mạ hơn via truyền thống, do đó:

- Cần bố trí hợp lý trong layout

- Phải tính toán sớm trong thiết kế stack-up

- Phù hợp với công nghệ khoan laser và ép nhiều lần

6.3. Cấu trúc stack-up

PCB HDI thường có stack-up phức tạp, gồm nhiều lớp đồng và điện môi. Stack-up phải được thiết kế sao cho:

- Đảm bảo độ bền cơ học

- Đáp ứng yêu cầu điện (SI/PI/EMI)

- Phù hợp với quy trình ép nhiều lần và khoan microvia

7. Một số lưu ý để tối ưu chi phí sản xuất mạch HDI

Hình 6. Quy trình sản xuất mạch HDI

Trong khi các sản phẩm điện tử ngày càng thu nhỏ kích thước, người dùng vẫn đặt chất lượng là yếu tố quan trọng hàng đầu, sau giá thành. Với thiết kế hợp lý, một PCB 8 lớp dùng via xuyên lỗ truyền thống có thể được thay thế bằng PCB HDI 4 lớp sử dụng microvia. Khả năng đi dây của PCB HDI 4 lớp hoàn toàn có thể đạt hoặc vượt hiệu năng của PCB 8 lớp thông thường. Mặc dù quy trình microvia làm tăng chi phí công nghệ, nhưng việc giảm số lớp và giảm diện tích bo mạch giúp giảm mạnh chi phí vật liệu và tổng chi phí hệ thống.Các yếu tố ảnh hưởng đến chi phí PCB HDI:

Để kiểm soát chi phí PCB HDI hiệu quả, cần cân nhắc:

- Via và lỗ khoan Via càng nhỏ → yêu cầu độ chính xác càng cao → chi phí tăng. Số lượng via nhiều → chi phí tăng

- Stack-up và số lớp: Stack-up càng phức tạp, số lớp càng nhiều → chi phí càng cao. Do vậy nên tối ưu để đạt hiệu năng cao nhất với số lớp ít nhất

- Vật liệu: Vật liệu lõi (FR4, high-Tg, metal core…) và xử lý bề mặt (HASL, ENIG, ENEPIG…) ảnh hưởng trực tiếp đến giá thành

- Số lần ép lớp (Lamination cycles): Nhiều lần ép → tăng độ tin cậy → tăng chi phí và thời gian

- Stacked vs. Staggered microvia: Via xếp chồng (Stacked) thường chi phí đắt hơn do khó xử lý tốn nhiều vật liệu và thời gian gia công lâu hơn.

- Kích thước pad: Tối ưu pad ngay từ đầu giúp giảm lỗi sản xuất cũng như chi phí chỉnh sửa.

8. Kết Luận

Mạch HDI (High Density Interconnect) đang trở thành xu hướng tất yếu trong ngành điện tử hiện đại nhờ khả năng tích hợp mật độ cao, kích thước nhỏ gọn, cải thiện toàn vẹn tín hiệu và tối ưu chi phí hệ thống. Với các công nghệ cốt lõi như microvia, via-in-pad, stack-up nhiều lớp và khoan laser, HDI PCB cho phép hiện thực hóa các sản phẩm tốc độ cao, hiệu năng cao và độ tin cậy cao trong các lĩnh vực như điện tử tiêu dùng, ô tô, y tế, công nghiệp và IoT. Việc chuẩn hóa tối ưu thiết kế bo mạch ngay từ đầu cũng như lựa chọn nhà cung cấp mạch in PCB có năng lực sẽ là yếu tố then chốt giúp doanh nghiệp khai thác tối đa lợi thế của công nghệ này và rút ngắn thời gian đưa sản phẩm ra thị trường.